#### NEO FORZA DDR5 32GB-5200 / 5600 / 6000 / 6400 RGB UDIMM

### **General Description**

This chapter gives an overview of the 288-pin DDR5 unbuffered dual in-line memory modules product family and describes its main characteristics.

#### **Features**

- 288-Pin RGB UDIMM (Lead-Free) DDR5 SDRAM Memory Module.

- Data transfer rates: PC5-41600 / 44800 / 48000 / 51200.

- Power supply: VDD: 1.067V ~ 1.166V.

XMP VDD: 5200@1.1V / 5600 @1.2V / 6000MHz @1.3V / 6400MHz @1.4V

- Module organization: 4096Meg × 64.

- DRAM organization: 2048Mb × 8.

- 32 internal banks; 8 groups of 4 banks each.

- 16-bit prefetch.

- BL16, BC8 OTF, BL32, BL32 OTF supported.

- DFE (Decision Feedback Equalization) for DQ.

- On-Die ECC.

- Same Bank Refresh.

- On Die Termination(ODT) via Mode Register setting.

- Connectivity Test (CT)

**Ordering Information for Compliant Products**

| Part Number         | Compliance Code                 | Number of<br>Ranks | DRAM<br>Organisation | # of<br>SDRAMs |  |

|---------------------|---------------------------------|--------------------|----------------------|----------------|--|

| NMGD532F82-5200JI20 | 32GB / XMP PC5-41600 / 40-40-40 | 2                  | 2Gb x8               | 16             |  |

| NMGD532F82-5600EI20 | 32GB / XMP PC5-44800 / 40-40-40 | 2                  | 2Gb x8               | 16             |  |

| NMGD532F82-6000LI20 | 32GB / XMP PC5-48000 / 40-40-40 | 2                  | 2Gb x8               | 16             |  |

| NMGD532F82-6400FI20 | 32GB / XMP PC5-51200 / 40-40-40 | 2                  | 2Gb x8               | 16             |  |

# **Pin Assignments**

|     | 288-Pin DDR5 UDIMM Front |     |                 |     |                 |     |                 | 288-Pin DDR5 UDIMM Back |                 |     |                 |     |                 |     |                 |

|-----|--------------------------|-----|-----------------|-----|-----------------|-----|-----------------|-------------------------|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| Pin | Symbol                   | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin                     | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

| 1   | VIN_BULK                 | 37  | DQ20_A          | 73  | CK0_A_c         | 109 | V <sub>SS</sub> | 145                     | VIN_BULK        | 181 | DQ22_A          | 217 | CK1_A_c         | 253 | V <sub>SS</sub> |

| 2   | RFU                      | 38  | V <sub>SS</sub> | 74  | V <sub>SS</sub> | 110 | DQ5_B           | 146                     | VIN_BULK        | 182 | V <sub>SS</sub> | 218 | V <sub>SS</sub> | 254 | DQ7_B           |

| 3   | RFU                      | 39  | DQ21_A          | 75  | RFU             | 111 | V <sub>SS</sub> | 147                     | PWR<br>GOOD     | 183 | DQ23_A          | 219 | RFU             | 255 | V <sub>SS</sub> |

| 4   | HSCL                     | 40  | V <sub>SS</sub> | 76  | RFU             | 112 | DQ8_B           | 148                     | HSA             | 184 | V <sub>SS</sub> | 220 | RFU             | 256 | DQ10_B          |

| 5   | HSDA                     | 41  | DQ24_A          | 77  | V <sub>SS</sub> | 113 | VSS             | 149                     | RFU             | 185 | DQ26_A          | 221 | V <sub>SS</sub> | 257 | V <sub>SS</sub> |

| 6   | V <sub>SS</sub>          | 42  | V <sub>SS</sub> | 78  | CK0_B_t         | 114 | DQ9_B           | 150                     | V <sub>SS</sub> | 186 | V <sub>SS</sub> | 222 | CK1_B_t         | 258 | DQ11_B          |

| 7   | RFU                      | 43  | DQ25_A          | 79  | CK0_B_c         | 115 | V <sub>SS</sub> | 151                     | PWR_EN          | 187 | DQ27_A          | 223 | CK1_B_c         | 259 | V <sub>SS</sub> |

| 8   | V <sub>SS</sub>          | 44  | V <sub>SS</sub> | 80  | V <sub>SS</sub> | 116 | DM1_B_n         | 152                     | RFU             | 188 | V <sub>SS</sub> | 224 | V <sub>SS</sub> | 260 | DQS1_B_c        |

| 9   | DQ0_A                    | 45  | DM3_A_n         | 81  | RFU             | 117 | V <sub>SS</sub> | 153                     | V <sub>SS</sub> | 189 | DQS3_A_c        | 225 | RFU             | 261 | DQS1_B_t        |

| 10  | V <sub>SS</sub>          | 46  | V <sub>SS</sub> | 82  | CA12_B          | 118 | DQ12_B          | 154                     | DQ2_A           | 190 | DQS3_A_t        | 226 | RFU             | 262 | V <sub>SS</sub> |

| 11  | DQ1_A                    | 47  | DQ28_A          | 83  | V <sub>SS</sub> | 119 | V <sub>SS</sub> | 155                     | V <sub>SS</sub> | 191 | V <sub>SS</sub> | 227 | V <sub>SS</sub> | 263 | DQ14_B          |

| 12  | V <sub>SS</sub>          | 48  | V <sub>SS</sub> | 84  | CA10_B          | 120 | DQ13_B          | 156                     | DQ3_A           | 192 | DQ30_A          | 228 | CA11_B          | 264 | V <sub>SS</sub> |

| 13  | DQS0_A_c                 | 49  | DQ29_A          | 85  | CA8_B           | 121 | V <sub>SS</sub> | 157                     | V <sub>SS</sub> | 193 | V <sub>SS</sub> | 229 | CA9_B           | 265 | DQ15_B          |

| 14  | DQS0_A_t                 | 50  | V <sub>SS</sub> | 86  | V <sub>SS</sub> | 122 | DQ16_B          | 158                     | DM0_A_n         | 194 | DQ31_A          | 230 | V <sub>SS</sub> | 266 | V <sub>SS</sub> |

| 15  | V <sub>SS</sub>          | 51  | CB0_A           | 87  | CA6_B           | 123 | V <sub>SS</sub> | 159                     | V <sub>SS</sub> | 195 | V <sub>SS</sub> | 231 | CA7_B           | 267 | DQ18_B          |

| 16  | DQ4_A                    | 52  | V <sub>SS</sub> | 88  | CA4_B           | 124 | DQ17_B          | 160                     | DQ6_A           | 196 | CB2_A           | 232 | CA5_B           | 268 | V <sub>SS</sub> |

| 17  | V <sub>SS</sub>          | 53  | CB1_A           | 89  | V <sub>SS</sub> | 125 | V <sub>SS</sub> | 161                     | V <sub>SS</sub> | 197 | V <sub>SS</sub> | 233 | V <sub>SS</sub> | 269 | DQ19_B          |

| 18  | DQ5_A                    | 54  | V <sub>SS</sub> | 90  | CA2_B           | 126 | DQS2_B_c        | 162                     | DQ7_A           | 198 | CB3_A           | 234 | CA3_B           | 270 | V <sub>SS</sub> |

| 19  | V <sub>SS</sub>          | 55  | DQS4_A_c        | 91  | CA0_B           | 127 | DQS2_B_t        | 163                     | V <sub>SS</sub> | 199 | V <sub>SS</sub> | 235 | CA1_B           | 271 | DM2_B_n         |

| 20  | DQ8_A                    | 56  | DQS4_A_t        | 92  | V <sub>SS</sub> | 128 | V <sub>SS</sub> | 164                     | DQ10_A          | 200 | ALERT_n         | 236 | V <sub>SS</sub> | 272 | V <sub>SS</sub> |

| 21  | V <sub>SS</sub>          | 57  | V <sub>SS</sub> | 93  | CS0_B_n         | 129 | DQ20_B          | 165                     | V <sub>SS</sub> | 201 | V <sub>SS</sub> | 237 | CS1_B_n         | 273 | DQ22_B          |

| 22  | DQ9_A                    | 58  | CS0_A_n         | 94  | V <sub>SS</sub> | 130 | V <sub>SS</sub> | 166                     | DQ11_A          | 202 | CS1_A_n         | 238 | V <sub>SS</sub> | 274 | V <sub>SS</sub> |

| 23  | V <sub>SS</sub>          | 59  | V <sub>SS</sub> | 95  | RESET_n         | 131 | DQ21_B          | 167                     | V <sub>SS</sub> | 203 | V <sub>SS</sub> | 239 | DQS4_B_c        | 275 | DQ23_B          |

| 24  | DM1_A_n                  | 60  | CA0_A           | 96  | V <sub>SS</sub> | 132 | V <sub>SS</sub> | 168                     | DQS1_A_c        | 204 | CA1_A           | 240 | DQS4_B_t        | 276 | V <sub>SS</sub> |

| 25  | V <sub>SS</sub>          | 61  | CA2_A           | 97  | CB0_B           | 133 | DQ24_B          | 169                     | DQS1_A_t        | 205 | CA3_A           | 241 | V <sub>SS</sub> | 277 | DQ26_B          |

| 26  | DQ12_A                   | 62  | V <sub>SS</sub> | 98  | V <sub>SS</sub> | 134 | V <sub>SS</sub> | 170                     | V <sub>SS</sub> | 206 | V <sub>SS</sub> | 242 | CB2_B           | 278 | V <sub>SS</sub> |

| 27  | VSS                      | 63  | CA4_A           | 99  | CB1_B           | 135 | DQ25_B          | 171                     | DQ14_A          | 207 | CA5_A           | 243 | V <sub>SS</sub> | 279 | DQ27_B          |

| 28  | DQ13_A                   | 64  | CA6_A           | 100 | VSS             | 136 | VSS             | 172                     | V <sub>SS</sub> | 208 | CA7_A           | 244 | CB3_B           | 280 | VSS             |

| 29  | V <sub>SS</sub>          | 65  | V <sub>SS</sub> | 101 | DQ0_B           | 137 | DM3_B_n         | 173                     | DQ15_A          | 209 | V <sub>SS</sub> | 245 | V <sub>SS</sub> | 281 | DQS3_B_c        |

| 30  | DQ16_A                   | 66  | CA8_A           | 102 | V <sub>SS</sub> | 138 | V <sub>SS</sub> | 174                     | V <sub>SS</sub> | 210 | CA9_A           | 246 | DQ2_B           | 282 | DQS3_B_t        |

| 31  | V <sub>SS</sub>          | 67  | CA10_A          | 103 | DQ1_B           | 139 | DQ28_B          | 175                     | DQ18_A          | 211 | CA11_A          | 247 | V <sub>SS</sub> | 283 | V <sub>SS</sub> |

| 32  | DQ17_A                   | 68  | V <sub>SS</sub> | 104 | V <sub>SS</sub> | 140 | V <sub>SS</sub> | 176                     | V <sub>SS</sub> | 212 | V <sub>SS</sub> | 248 | DQ3_B           | 284 | DQ30_B          |

| 33  | V <sub>SS</sub>          | 69  | CA12_A          | 105 | DQS0_B_c        | 141 | DQ29_B          | 177                     | DQ19_A          | 213 | RFU             | 249 | V <sub>SS</sub> | 285 | V <sub>SS</sub> |

| 34  | DQS2_A_c                 | 70  | RFU             | 106 | DQS0_B_t        | 142 | V <sub>SS</sub> | 178                     | V <sub>SS</sub> | 214 | RFU             | 250 | DM0_B_n         | 286 | DQ31_B          |

| 35  | DQS2_A_t                 | 71  | V <sub>SS</sub> | 107 | V <sub>SS</sub> | 143 | RFU             | 179                     | DM2_A_n         | 215 | V <sub>SS</sub> | 251 | V <sub>SS</sub> | 287 | V <sub>SS</sub> |

# **Pin Assignments (Continued)**

|   | 288-Pin DDR5 UDIMM Front |                 |     |         |     |        |     | 2      | 88-Pin DDR5 | UDIM            | M Back |         |     |        |     |        |

|---|--------------------------|-----------------|-----|---------|-----|--------|-----|--------|-------------|-----------------|--------|---------|-----|--------|-----|--------|

|   | Pin                      | Symbol          | Pin | Symbol  | Pin | Symbol | Pin | Symbol | Pin         | Symbol          | Pin    | Symbol  | Pin | Symbol | Pin | Symbol |

| Γ | 36                       | V <sub>SS</sub> | 72  | CK0_A_t | 108 | DQ4_B  | 144 | RFU    | 180         | V <sub>SS</sub> | 216    | CK1_A_t | 252 | DQ6_B  | 288 | RFU    |

**Pin Descriptions**

| Pili Descriptions                     |                                                      |  |  |  |  |  |

|---------------------------------------|------------------------------------------------------|--|--|--|--|--|

| Symbol                                | Description                                          |  |  |  |  |  |

| CA0_A - CA12_A,                       | SDRAM Command / Address bus                          |  |  |  |  |  |

| CA0_B - CA12_B                        | SDIVAM Command / Address bus                         |  |  |  |  |  |

| CS0_A_n - CS1_A_n,                    | SDRAM Chin Salact                                    |  |  |  |  |  |

| CS0_B_n - CS1_B_n                     | SDRAM Chip Select                                    |  |  |  |  |  |

| DQ0_A - DQ31_A,                       | DIMM moment data bus                                 |  |  |  |  |  |

| DQ0_B - DQ31_B,                       | DIMM memory data bus                                 |  |  |  |  |  |

| CB0_A - CB3_A,                        | DIMM FCC abook hits                                  |  |  |  |  |  |

| CB0_B - CB3_B                         | DIMM ECC check bits                                  |  |  |  |  |  |

| DQS0_A_t - DQS4_A_t,                  | SDRAM data strobes                                   |  |  |  |  |  |

| DQS0_B_t - DQS4_B_t                   | (positive line of differential pair)                 |  |  |  |  |  |

| DQS0_A_c - DQS4_A_c,                  | SDRAM data strobes                                   |  |  |  |  |  |

| DQS0_B_c - DQS4_B_c                   | (negative line of differential pair)                 |  |  |  |  |  |

| DM0_A_n – DM3_A_n,                    | SDRAM data masks                                     |  |  |  |  |  |

| DM0_B_n - DM3_B_n                     | SDRAW data masks                                     |  |  |  |  |  |

| CK0_A_t, CK1_A_t,                     | SDRAM clocks                                         |  |  |  |  |  |

| CK0_B_t, CK1_B_t                      | (positive line of differential pair)                 |  |  |  |  |  |

| СК0_A_с, СК1_A_с,<br>СК0_B_с, СК1_B_с | SDRAM clocks<br>(negative line of differential pair) |  |  |  |  |  |

| Symbol   | Description                                           |  |  |  |  |  |

|----------|-------------------------------------------------------|--|--|--|--|--|

| HSCL     | SidebandBus clock                                     |  |  |  |  |  |

| HSDA     | SidebandBus data                                      |  |  |  |  |  |

| HAS      | SidebandBus address                                   |  |  |  |  |  |

| ALERT_n  | SDRAM ALERT_n                                         |  |  |  |  |  |

| RESET_n  | Set DRAMs to a known state                            |  |  |  |  |  |

| Vin_BULK | 5V power input supply to the PMIC for analog circuits |  |  |  |  |  |

| Vss      | Power supply return (ground)                          |  |  |  |  |  |

| PWR_GOOD | Power good indicator                                  |  |  |  |  |  |

| PWR_EN   | PMIC Enable                                           |  |  |  |  |  |

| RFU      | Reserved for future use                               |  |  |  |  |  |

#### Note:

DDR5 UDIMM has 2 channels (channel-A and channel-B) of signal bus.

The signals with suffix:\_A (e.g. DQ0\_A) are for channel-A, and the signals with suffix:\_B (e.g. DQ0\_B) are for channel-B

**DIMM Voltage Requirements**

| Symbol                | D                          | Volta | age Ratin | g (V) | Maximum                 | Dawer State |  |

|-----------------------|----------------------------|-------|-----------|-------|-------------------------|-------------|--|

|                       | Parameter                  | Min.  | TYP.      | Max.  | Expected<br>Current (A) | Power State |  |

| V <sub>IN</sub> _BULK | Host Supply Voltage        | 4.25  | 5.0       | 5.5   | 2.5 / 2.0               | Operational |  |

| SWA, SWB              | PMIC Output Supply Voltage | -     | 1.1       | -     | 6                       | Operational |  |

| SWA+SWB               | PMIC Output Supply Voltage | -     | 1.1       | -     | 12                      | Operational |  |

| SWC                   | PMIC Output Supply Voltage | -     | 1.8       | -     | 2                       | Operational |  |

| 1.8V LDO              | PMIC Output Supply Voltage | -     | 1.8       | -     | 0.025                   | Operational |  |

| 1.0V LDO              | PMIC Output Supply Voltage | -     | 1.0       | -     | 0.020                   | Operational |  |

#### Note:

- 1. During first power on the input voltage supply must reach minimum 4.25V for PMIC to detect valid input supply.

- 2. The ramp up rate between 300 mV and 4.0V.

- 3. The ramp down rate between 4V and 300 mV.

- 4. The area under the curve above  $V_{IN}$ \_Bulk = TBD V.  $V_{IN}$ \_Bulk\_AC spec must also be satisfied.

- 5. The minimum input current requirement is to deliver the maximum output current on V<sub>OUT</sub>\_1.8V and V<sub>OUT</sub>\_1.0V LDO plus the current.

- V<sub>IN</sub>\_Bulk = 5.0V. Measured at room temperature. All circuitry including output regulators and LDOs are off. VR\_EN signal is static.

- 7.  $V_{\text{IN}}^{}$ Bulk = 5.0V. Measured at room temperature. All output requlators and LDOs are on with 0 A output load..  $\overline{\text{VR}}_{}$ EN signal is static.

- 8. 20MHz bandwidth limited measurement for all voltage in the table.

- 9. Voltages are measured at the DIMM gold fingers and at PMIC output pins.

- 10. The SDRAM specification must be met and take precedence over this document.

- 11. Maximum current establishes the plaform maximum current regulation point. It provides a data point for DIMM developers ro set power plane impedances.

- 12. Typical voltage is platform dependent. This is a suggested calue only.

- 13. Follow JEDEC specification.

**Recommended Operating Temperature Ranges**

| Symbol | Parameter                             | Rating  | Units | Notes |

|--------|---------------------------------------|---------|-------|-------|

| Topr   | Normal Operating Temperature Range    | 0 ~ 85  | °C    | 1,2   |

|        | Extended Temperature Range (Optional) | 85 ~ 95 | °C    | 1,3   |

#### Note:

- The operating temperature is the case surface temperature on the center-top side of the DDR5 device. For measurements conditions, refer to JESD51-2.

- 2. Normal is themaximum limit when device is operationg in the Normal Temperature Mode.

- 3. Extended is the maximum limit when device is operating in the Extended Temperature Mode.

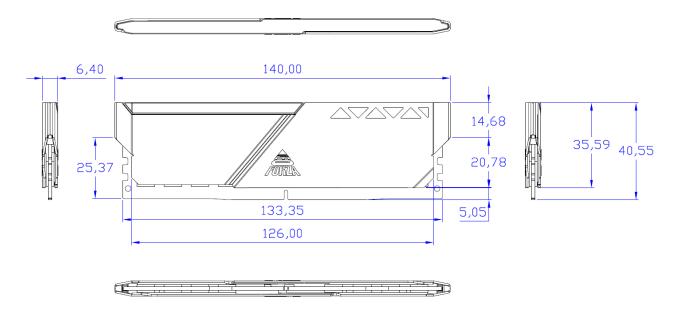

# **Physical Dimensions (PCB with Heatsink)**

Note: 1. All dimensions are in millimeters; MAX/MIN or typical (TYP) where noted.

- 2. Tolerance on all dimensions ±0.3 unless otherwise specified.

- 3. The dimensional diagram is for reference only.

## **Packing Box**

Front side Back side

Note: The specification stickers on the package are for reference only.

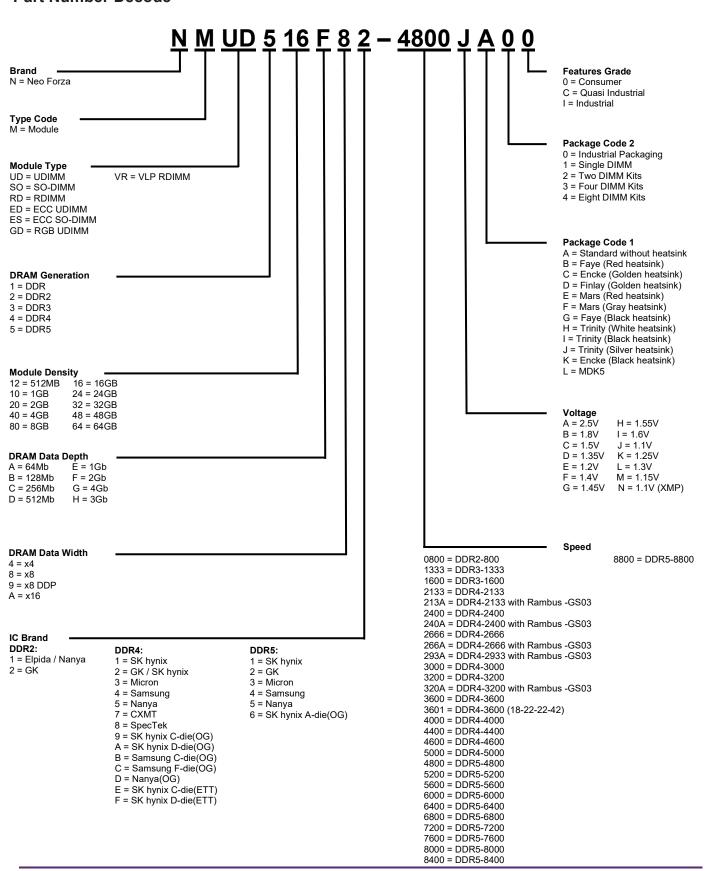

#### **Part Number Decode**